Home Search Collections Journals About Contact us My IOPscience

An introduction to InP-based generic integration technology

This content has been downloaded from IOPscience. Please scroll down to see the full text. 2014 Semicond. Sci. Technol. 29 083001 (http://iopscience.iop.org/0268-1242/29/8/083001) View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 131.111.184.102 This content was downloaded on 11/07/2014 at 10:29

Please note that terms and conditions apply.

Semicond. Sci. Technol. 29 (2014) 083001 (41pp)

# **Invited Review**

# An introduction to InP-based generic integration technology

Meint Smit<sup>1</sup>, Xaveer Leijtens<sup>1</sup>, Huub Ambrosius<sup>1</sup>, Erwin Bente<sup>1</sup>, Jos van der Tol<sup>1</sup>, Barry Smalbrugge<sup>1</sup>, Tjibbe de Vries<sup>1</sup>, Erik-Jan Geluk<sup>1</sup>, Jeroen Bolk<sup>1</sup>, Rene van Veldhoven<sup>1</sup>, Luc Augustin<sup>1,4</sup>, Peter Thijs<sup>1,4</sup>, Domenico D'Agostino<sup>1</sup>, Hadi Rabbani<sup>1</sup>, Katarzyna Lawniczuk<sup>1,12</sup>, Stanislaw Stopinski<sup>1,2</sup>, Saeed Tahvill<sup>1</sup>, Antonio Corradi<sup>1</sup>, Emil Kleijn<sup>1</sup>, Dzmitry Dzibrou<sup>1</sup>, Manuela Felicetti<sup>1</sup>, Elton Bitincka<sup>1</sup>, Valentina Moskalenko<sup>1</sup>, Jing Zhao<sup>1</sup>, Rui Santos<sup>1</sup>, Giovanni Gilardi<sup>1</sup>, Weiming Yao<sup>1</sup>, Kevin Williams<sup>1</sup>, Patty Stabile<sup>1</sup>, Piet Kuindersma<sup>1</sup>, Josselin Pello<sup>1</sup>, Srivathsa Bhat<sup>1</sup>, Yuqing Jiao<sup>1</sup>, Dominik Heiss<sup>1</sup>, Gunther Roelkens<sup>1,11</sup>, Mike Wale<sup>1,2</sup>, Paul Firth<sup>2</sup>, Francisco Soares<sup>3</sup>, Norbert Grote<sup>3</sup>, Martin Schell<sup>3</sup>, Helene Debregeas<sup>5</sup>, Mohand Achouche<sup>5</sup>, Jean-Louis Gentner<sup>5</sup>, Arjen Bakker<sup>6</sup>, Twan Korthorst<sup>6</sup>, Dominic Gallagher<sup>7</sup>, Andrew Dabbs<sup>7</sup>, Andrea Melloni<sup>8,9</sup>, Francesco Morichetti<sup>9</sup>, Daniele Melati<sup>9</sup>, Adrian Wonfor<sup>10</sup>, Richard Penty<sup>10</sup>, Ronald Broeke<sup>3</sup>, Bob Musk<sup>4,5</sup> and Dave Robbins<sup>6</sup>

- <sup>1</sup>Eindhoven University of Technology—COBRA Research Institute, Eindhoven, The Netherlands

- <sup>2</sup>Oclaro, Caswell, Northamptonshire, UK

- <sup>3</sup> Fraunhofer Heinrich Hertz Institut, Berlin, Germany

- <sup>4</sup> SMART Photonics, Eindhoven, The Netherlands

- <sup>5</sup> 3–5 Lab, Marcoussis, France

- <sup>6</sup>Phoenix Software, Enschede, The Netherlands

- <sup>7</sup> Photon Design, Oxford, UK

- <sup>8</sup> Filarete, Milano, Italy

- <sup>9</sup> Politecnico di Milano, Italy

- <sup>10</sup> University of Cambridge, UK

- <sup>11</sup>Ghent University/IMEC, Ghent, Belgium

- <sup>12</sup> Warsaw University of Technology, IMIO, Warsaw, Poland

- <sup>13</sup> Bright Photonics, Maarssen, The Netherlands

- <sup>14</sup>Gooch and Housego, Torquay, Devon, UK

- <sup>15</sup> Entroptix, Kingsbridge, Devon, UK

- <sup>16</sup>Willow Photonics, Abthorpe, Northampton, UK

E-mail: m.k.smit@tue.nl

Received 14 January 2014, revised 25 March 2014 Accepted for publication 10 April 2014 Published 13 June 2014

# Abstract

Photonic integrated circuits (PICs) are considered as the way to make photonic systems or subsystems cheap and ubiquitous. PICs still are several orders of magnitude more expensive than their microelectronic counterparts, which has restricted their application to a few niche markets.

Content from this work may be used under the terms of the Creative Commons Attribution 3.0 licence. Any further distribution of this work must maintain attribution to the author(s) and the title of the work, journal citation and DOI.

Recently, a novel approach in photonic integration is emerging which will reduce the R&D and prototyping costs and the throughput time of PICs by more than an order of magnitude. It will bring the application of PICs that integrate complex and advanced photonic functionality on a single chip within reach for a large number of small and larger companies and initiate a breakthrough in the application of Photonic ICs. The paper explains the concept of generic photonic integration technology using the technology developed by the COBRA research institute of TU Eindhoven as an example, and it describes the current status and prospects of generic InP-based integration technology.

Keywords: photonic integration, InP, photonic IC, generic foundry

(Some figures may appear in colour only in the online journal)

#### 1. Background

#### 1.1. History of photonic integration

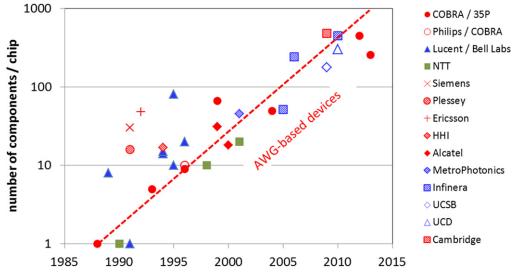

After its first appearance in the published literature over forty years ago [1], it was believed that microphotonic integration would take a similar development path to that followed by microelectronic integration. In his review paper of 1977 Tien [2] mentioned as one of the major goals of microphotonic integration or 'Integrated Optics' as it was called at the time: 'the integration of a large number of optical devices on a small substrate, so forming an optical circuit reminiscent of the integrated circuit in microelectronics'. In the following years a number of chips of increasing complexity were reported. Figure 1 shows the complexity development measured as the number of components integrated on a single chip<sup>17</sup>. The underlying data is summarized in table 1 and briefly described below.

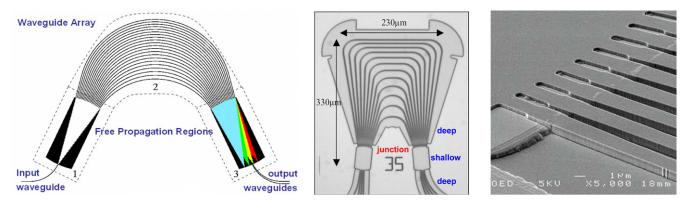

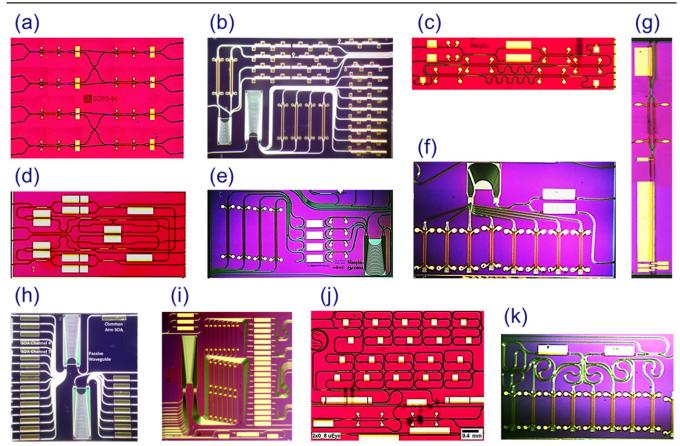

Early examples of complex InP-based photonic integrated circuits (PICs)<sup>18</sup> are a WDM source by Koren [3], integrating three lasers consisting of a semiconductor optical amplifier (SOA) and a tunable Bragg Grating Reflector, with a power combiner and a booster SOA on a single chip; a grating-based receiver by Cremer [4], integrating an Echelle grating demultiplexer with more than 30 detectors; a 4×4 cross-bar switch by Duthie [5], integrating 16 reverse- $\Delta\beta$ switches; a switch array by Gustavsson [6], integrating 24 SOA gate switches with 24 1×2 couplers; and a polarization diversity heterodyne receiver by Kaiser [7], integrating a DBR-type local oscillator laser with polarization mode splitters, polarization mode filters, 3 dB combiners, detector diodes in balanced configuration, junction FETs and load resistors. The highest complexities so far have been reported in AWG-based PICs. It started with the publication of the first AWG by Smit [8] in 1988, followed by Takahashi [9] and Dragone [10]. After the invention of the AWG a number of AWG-based devices with increasing circuit complexity were reported: WDM receivers with 5–10 components by Amersfoort [11], Zirngibl [12] and Steenbergen [13]; WDM lasers with 10–20 components by Zirngibl [14, 15] and Staring [16]; WDM channel selectors with 10–20 components by Zirngibl [14, 15] and Kikuchi [21] and a cross-connect chip with 66 components by Herben [22]. A special device is the WDM-receiver with integrated preamplifiers by Chandrasekhar [23] which counts 81 components, most of them electronic (transistors and resistors).

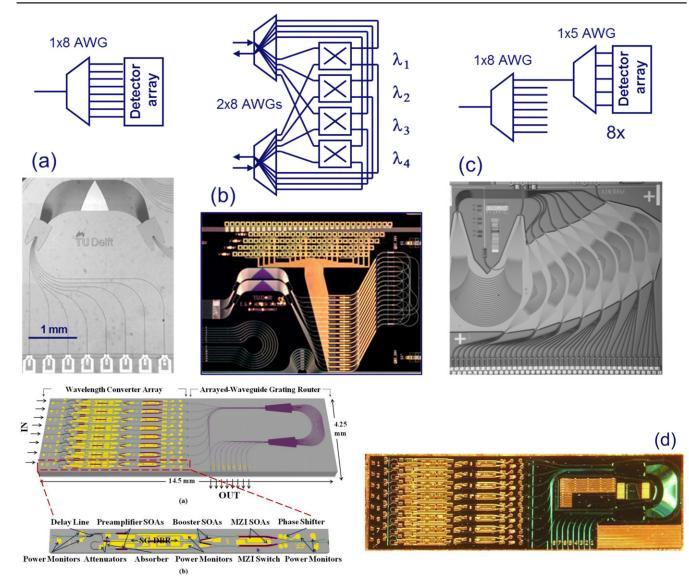

Figure 2 illustrates two of these WDM devices: a WDM receiver with nine components (figure 2(a)) and a WDM cross-connect with 66 components (figure 2(b)).

The new century brought a significant increase in complexity: WDM receiver and transmitter chips with 44-51 components by Tolstikhin [24], Three-FivePhotonics [25] and Infinera [26]. Shortly after, in 2006, Infinera published a 40channel WDM transmitter with 241 components [27]. Figure 2(c) illustrates the 40-channel WDM monitor chip with 49 components [25] and figure 2(d) an  $8 \times 8$  wavelength router chip with 175 components reported by Nicholes in 2009 [28]. In the same year Wang [29] reported a  $16 \times 16$ SOA switch matrix with 480 components fabricated in an allactive wafer, and one year later Soares [30] a 100-channel Arbitrary Waveform Generator with more than 300 components. The latter device also contains 400 phase shifters for reducing the high cross-talk level in the very large AWG which is used to separate 100 wavelength channels. Two PICs with more than 450 components fabricated in an advanced active-passive integration technology have been reported by Corzine (Infinera) [31] and Stabile (COBRA) [32]. Stabile also reported an 8×8 wavelength switch with 256 components [33]. Table 1 gives an overview of the devices mentioned. An excellent overview of High Performance InP-Based Photonic ICs is given by Coldren [34].

In microelectronics there is a clear exponential development in the number of transistors per chip, which has been doubling every two years on average during the last four

<sup>&</sup>lt;sup>17</sup> Several metrics have been proposed for measuring chip complexity. We use a simple but coarse approach in which we count the number of basic components like AWGs, MMIs, SOAs, detectors and modulators. It does not count for the fact that a DFB laser is more complex than an MMI coupler, for example, so a higher number of components does not always mean a more complex chip. Further, we count only components that are essential for the PIC-functionality (e.g. no spare components that are not used).

$<sup>^{18}</sup>$  A full list of the abbreviations used in this review is given in the appendix.

decades. This phenomenon is known as Moore's law [35, 36]. Figure 1 reveals a similar development in microphotonics, albeit in an early stage and with a much larger scatter than its microelectronic counterpart. If we restrict ourselves to devices based on AWGs, with a more or less comparable technology (AWGs with integrated amplifiers and/or detectors) most of the outliers disappear, however, which suggests that photonic integration is taking a similar development path to microelectronics, probably driven by the same improvements in process equipment.

#### 1.2. Generic photonic integration technology

Despite similarities in the development of chip complexity there is, however, a marked difference between today's microphotonics and microelectronics, and that is in the R&D methodology followed. In microphotonics most integration technologies are developed and optimized for a specific application. As a result we have almost as many technologies as applications, most of them very similar, but sufficiently different to prevent easy transfer of a design from one fab to another. Owing to this huge fragmentation, the market for many of these application-specific technologies is too small to justify their further development into a low-cost industrial volume manufacturing process. And as a result the chip costs remain too high to find wide application.

This is quite different from microelectronics where a huge market is served by a small set of integration processes (most of them CMOS processes). In these processes a broad range of functionalities can be realized from a small set of basic building blocks (BBBs), like transistors, resistors, capacitors and interconnection tracks. By connecting these building blocks in different numbers and topologies we can realize a huge variety of circuits and systems, with complexities ranging from a few hundred up to over a billion transistors. We call such a process, in which a broad range of functionalities can be synthesized from a small set of BBBs, a *generic integration process*.

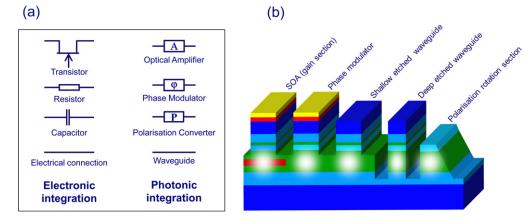

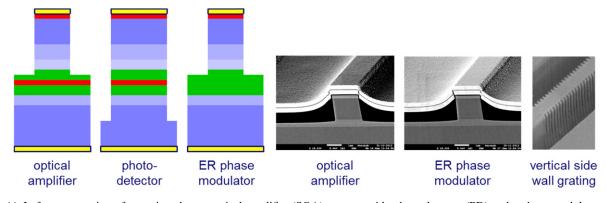

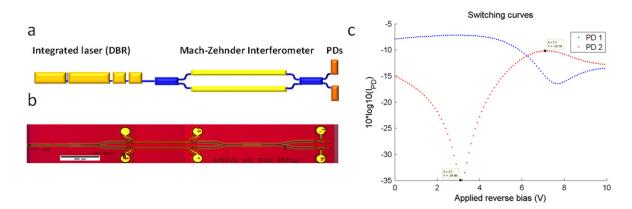

In photonics we can do something similar, as illustrated in figure 3(a). An integration process with building blocks for controlling the basic properties of light: the amplitude, the phase and the polarization, can support a broad range of functionalities. Figure 3(b) shows a schematic picture of five different components integrated in a single generic integration process on an InP substrate. The example is taken from the process of the COBRA research institute of TU Eindhoven. The green layer is the waveguide layer that carries the optical waveguide modes (indicated by a white spot); the dark red layer in the centre of the waveguide layer is the optically active gain medium. With a good waveguide structure we can make interconnections, but also passive components like couplers, filters and demultiplexers. With optical amplifiers (SOA), phase modulators and polarization converters, for manipulating the amplitude, the phase and the polarization of the light, the technology can support a broad range of functionalities, as illustrated in figure 4.

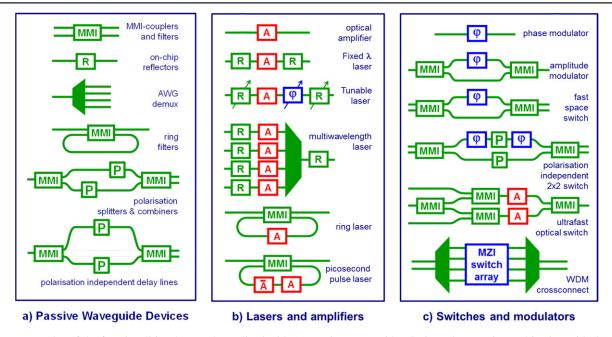

Figure 4(a) shows a few components that we can make with passive waveguides. The most important ones are MMI-

couplers and AWG-demultiplexers. With deep-etched strongconfinement waveguides we can make MMI-reflectors and compact ring filters. Another important building block that we can make in a passive waveguide is a polarization converter. By placing it appropriately in a Mach–Zehnder interferometer (MZI) we can make polarization splitters and combiners, and by placing it halfway a polarization dependent component, the response of this component becomes polarization independent.

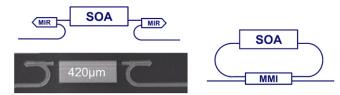

SOAs in combination with passive devices offer a broad range of functionalities, as illustrated in figure 4(b): Fabry— Perot (FP) lasers, multiwavelength lasers, ring lasers and, when used in combination with a wavelength tunable reflector, also tunable lasers. By using a short SOA section in reverse bias as a saturable absorber we can make picosecond pulse lasers. And a SOA in reverse bias can also be used as a detector.

Figure 4(c) illustrates some of the functionalities that we can make by combining phase modulators with passive devices: amplitude modulators, space switches, wavelength selective switches, such as WDM cross-connects and add-drop multiplexers. And by making use of the nonlinear properties of SOAs integrated in an MZI we can make ultrafast switches.

An advantage of generic integration technologies is that because they serve many different applications, they justify the investments in developing the technology for a very high performance and reliability at the level of the building blocks. This will make circuits realized in such a technology highly competitive. A single generic process will not be suited to all applications, of course. Just like in microelectronics we will need a few different generic technologies, optimized for different kinds of applications. But the number of generic technologies can be small, much smaller than the variety in today's technologies.

Further, in a standardized technology we can develop design libraries and a related software infrastructure for components or subcircuits that are used by many designers. This leads to a significant reduction of the design time and an increase in the design accuracy, so that fewer design cycles will be necessary to arrive at a required performance.

All this brings a fundamental change in the business model of photonics and allows commercial and academic groups to co-operate and move forward rather than forever reinventing the wheel.

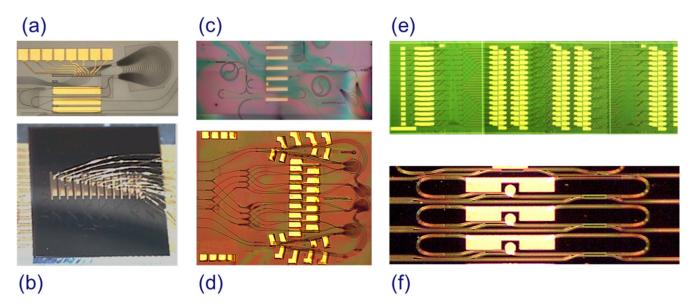

#### 1.3. Multi-project wafer runs

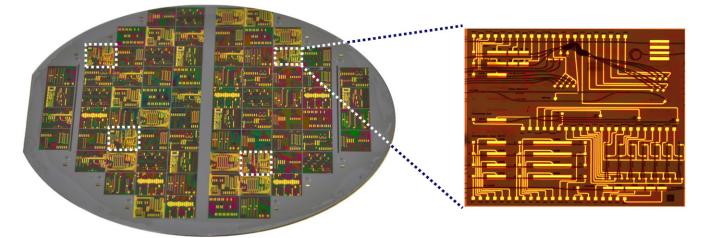

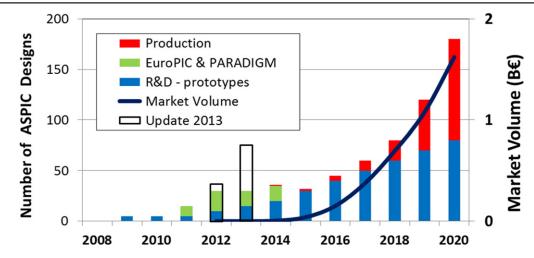

An important advantage of generic integration technology is that a number of different designs can be combined on the same wafer, because they all use the same fabrication process. Such a wafer is called a Multi-Project Wafer (MPW). And the Photonic ICs fabricated in such an MPW run are called ASPICs: Application Specific Photonic ICs, the photonic equivalent of an ASIC. ASPICs are application-specific PICs, realized in a standardized generic process. Figure 5 illustrates how a number of designs are combined on a single wafer. In this example there are 12 different designs; each

Figure 1. Development of chip complexity measured as the number of components per chip.

Table 1. Development of chip complexity measured as the number of components (#Comp) per chip. The last column refers to the references listed at the end of this article.

| Year | #Comp | Short Title                    | 1st Author    | Institute      | References         |

|------|-------|--------------------------------|---------------|----------------|--------------------|

| 1988 | 1     | AWG Smit COBRA                 |               | COBRA          | [8]                |

| 1989 | 8     | WDM source                     | Koren         | Bell Labs      | [3]                |

| 1990 | 1     | AWG                            | Takahashi     | NTT            | [ <mark>9</mark> ] |

| 1991 | 30    | Grating Spectrograph           | Cremer        | Siemens        | [4]                |

| 1991 | 1     | AWG                            | Dragone       | Bell Labs      | [10]               |

| 1991 | 16    | 4×4 Cross-bar switch           | Duthie        | Plessey        | [5]                |

| 1992 | 48    | Switch Array                   | Gustavsson    | Ericsson       | [ <mark>6</mark> ] |

| 1993 | 5     | WDM receiver                   | Amersfoort    | COBRA          | [11]               |

| 1994 | 17    | Heterodyne receiver            | Kaiser        | HHI            | [7]                |

| 1994 | 14    | WDM laser                      | Zirngibl      | Bell Labs      | [14]               |

| 1994 | 15    | WDM channel selector           | Zirngibl      | Bell Labs      | [17]               |

| 1995 | 10    | WDM receiver                   | Zirngibl      | Bell Labs      | [12]               |

| 1995 | 81    | WDM receiver & preamp          | Chandrasekhar | Bell Labs      | [23]               |

| 1996 | 9     | WDM receiver                   | Steenbergen   | COBRA          | [13]               |

| 1996 | 20    | WDM laser                      | Zirngibl      | Lucent         | [15]               |

| 1996 | 10    | WDM laser                      | Staring       | Philips        | [16]               |

| 1998 | 10    | WDM channel selector           | Ishii         | NTT            | [18]               |

| 1999 | 66    | WDM cross-connect              | Herben        | COBRA          | [22]               |

| 1999 | 31    | WDM laser                      | Ménézo        | Alcatel        | [19]               |

| 2000 | 18    | WDM channel selector           | Mestric       | Alcatel        | [20]               |

| 2001 | 20    | WDM channel selector           | Kikuchi       | NTT            | [21]               |

| 2003 | 45    | WDM receiver                   | Tolstikhin    | MetroPhotonics | [24]               |

| 2004 | 49    | WDM receiver                   | 35 Photonics  | 35Photonics    | [25]               |

| 2005 | 51    | WDM transmitter                | Nagarajan     | Infinera       | [26]               |

| 2006 | 240   | WDM transmitter                | Nagarajan     | Infinera       | [27]               |

| 2009 | 177   | Tunable WDM router             | Nicholes      | UCSB           | [28]               |

| 2009 | 480   | $16 \times 16$ SOA switch      | Wang          | UCAM           | [29]               |

| 2010 | 302   | Arb. Waveform Generator        | Soares        | UCD            | [30]               |

| 2010 | 450   | PM-DQPSK WDM transm            | Corzine       | Infinera       | [31]               |

| 2012 | 480   | $16 \times 16$ switch          | Stabile       | COBRA          | [32]               |

| 2013 | 256   | $8 \times 8$ wavelength switch | Stabile       | COBRA          | [33]               |

design is repeated four times. So from each wafer in an MPW batch, the designer will receive four chips. This approach leads to a large reduction of the research and development costs. In the development stage often a few design and fabrication cycles are necessary to arrive at the required performance. Usually a few chips out of the wafer are sufficient for testing the design in this stage. By combining a number of designs on a single wafer every designer gets a few

**Figure 2.** Examples of Photonic ICs: (a) a WDM receiver consisting of an AWG integrated with 8 detector diodes [13]; (b) a 4-channel  $2 \times 2$  WDM cross-connect integrating 2 AWGs with 16 Mach–Zehnder interferometer switches in dilated configuration (66 components in total); (c) a 40-channel WDM monitor chip integrating 9 AWGs and 40 detector diodes [25]; (d) an  $8 \times 8$  channel wavelength router, integrating 8 wavelength converter circuits with an  $8 \times 8$  AWG, with over 175 components [28].

chips and the costs of the run can be shared by all participants in the MPW-run. This will lead to a more-than-ten-fold reduction of the costs of a design run.

#### 1.4. Generic foundry model

The generic integration approach will lead to a large cost reduction by developing different products in a single or a few highly standardized processes. However, if the owner of the process does not provide access to external users the number of companies that can take advantage of this approach remains restricted. The corner stone of the generic foundry model is, therefore, the generic foundry: a chip manufacturer that provides open access to its generic integration process (es). In silicon microelectronics a number of chip manufacturers are providing such foundry access. In Photonics the generic foundry model is new.

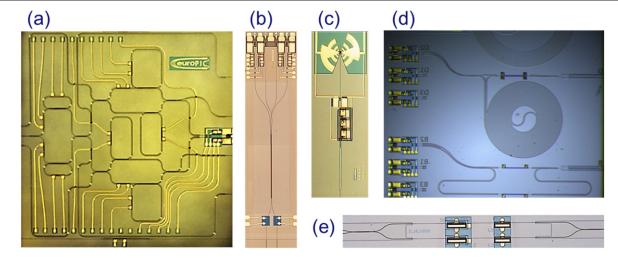

The COBRA research institute of TU Eindhoven has been pioneering generic photonic integration technology since the beginning of the century [37]. The generic approach gained momentum in the European Network of Excellence ePIXnet [38], in which more than 63 research groups active in the field of photonic integration were cooperating in the period from 2004–2009 on a number of photonic integration technologies. InP-based generic photonic integration technology has been explored in a number of European and national projects<sup>19</sup>. Access to InP-based generic foundry

<sup>&</sup>lt;sup>19</sup> The FP7 European projects EuroPIC [39] and PARADIGM [40], and the Dutch national projects MEMPHIS [41], IOP Photonic Devices [42] and STW GTIP: Generic Technologies in Integrated Photonics [43].

**Figure 3.** (a) Basic building blocks in generic electronic and photonic integration processes. (b) Schematic cross-section of the basic building blocks in a generic photonic integration process.

processes is organized by the JePPIX platform [44], in which Europe's key players in the field of InP-based photonic integration technology are cooperating. A more detailed description of the InP-based generic foundry approach is given in Smit *et al* [45]. At present (semi-) commercial access to InP-based generic foundry processes is offered by three chip manufacturers: the UK-based company Oclaro, the Fraunhofer Heinrich Hertz Institut in Berlin and the COBRA spinoff company SMART Photonics, located in Eindhoven, the Netherlands, which is commercializing the COBRA process.

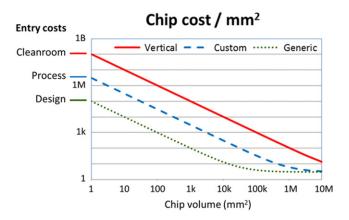

Figure 6 gives a (strongly simplified) explanation how the entry costs are reduced by the introduction of the generic foundry approach. In a vertical integrated fab model the component manufacturer owns the cleanroom facilities. The costs of a well-equipped cleanroom fab for fabrication of Photonic ICs are in the order of one or even a few hundred million Euros (or dollars) for advanced fabs. As shown in figure 6 chip volumes in excess of 10 million mm<sup>2</sup> (2500 3" wafers) are required to bring the investment cost per chip below  $10 \notin /mm^2$ . A chip with moderate complexity measures  $10-30 \text{ mm}^2$ , so at this price level about one million chips are required for return of investment. Such investments are only affordable technology market-dominant, top-tier for companies.

A few cleanroom owners provide access to fabless customers in order to share the burden of the cleanroom operational expenditure. In this way a fabless customer can avoid the huge investment in a fab and restrict investment to just the development costs of a specific integration process for a specific PIC. We call this model the custom foundry model: the foundry develops application-specific processes for customized PICs. For PICs of moderate complexity the process development costs, including process qualification, are in the order of a million up to a few million Euros and the level of  $10 \notin / \text{mm}^2$  is reached at volumes of a few times 10 000 chips (the second curve in figure 6 labelled custom). These are still significant volumes and the investment costs in combination with the risk are prohibitive for most small and medium enterprises (SMEs).

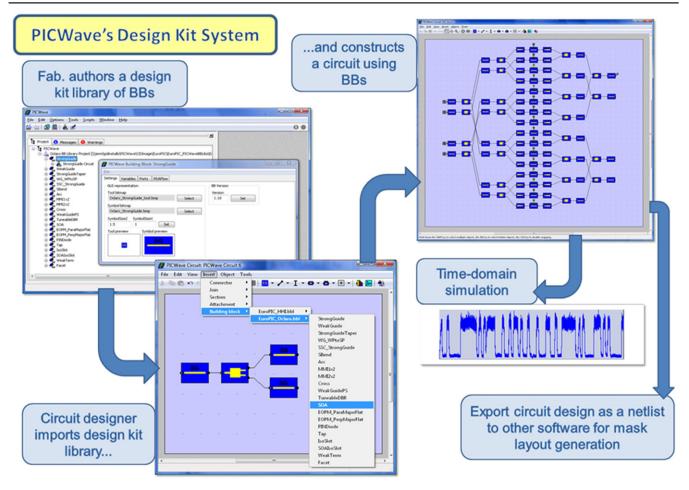

A dramatic further cost reduction can be achieved if the chip design is based on a generic (standardized) integration process, the development costs of which can be shared by many users. Then the entry costs are mainly restricted to design costs, which can be in the order of 100 k€. The design costs can be reduced even further by development of dedicated process design kits (PDKs) with component libraries that contain the mask layout and accurate models of the building blocks in the foundry platform. This will lead to both a reduction of the design time and the number of design cycles required to arrive at the required performance. In this approach, the cost level of  $10 \notin m^2$  can already be reached at volumes of 1000 chips (the third curve in figure 6 labelled generic). It will make entry costs for development of Photonic ICs affordable for most SMEs. We expect, as a consequence, that the introduction of the generic model will lead to a rapid expansion in the application of Photonic ICs.

#### 2. Generic integration process

There are many kinds of application-specific integration technologies, but also for the more generic technologies there is a large freedom in integration concepts, and different foundries will have different integration technologies, even if they are functionally equivalent. In this section we will explain the basics of a generic photonic integration process using the COBRA process as a representative example; it was the first generic process that offered an MPW service and most of the process and building block information is already in the public domain.

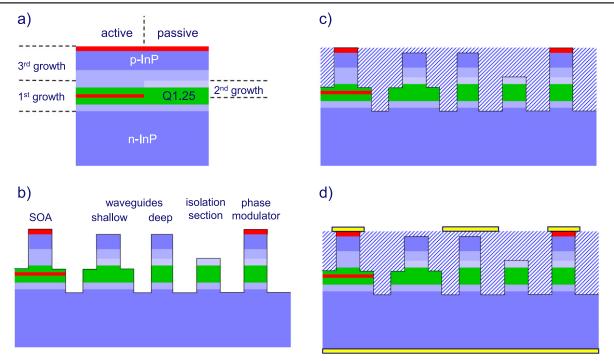

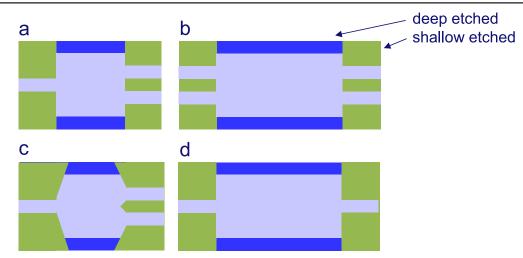

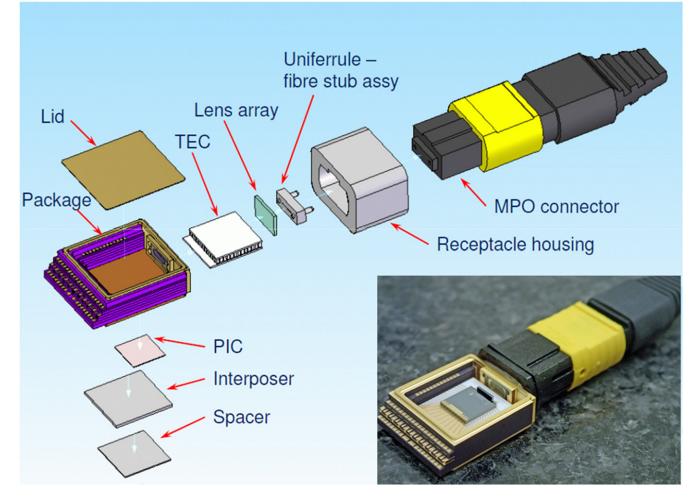

The integration process can roughly be subdivided into four process modules, which are illustrated in figure 8 and will be described below in broad outline. We will also indicate some new developments that are presently underway or planned for the continued evolution in generic processes at the JePPIX foundries Oclaro, Fraunhofer HHI and SMART Photonics.

**Figure 4.** Examples of the functionalities that can be realized with (a) passive waveguides devices alone, or in combination with (b) optical amplifiers and (c) phase modulators.

#### 2.1. Epitaxial growth

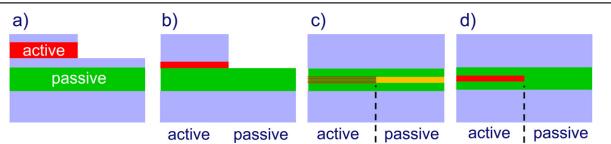

For the integration of active (amplifier) and passive (transparent waveguide) materials a number of integration schemes have been reported, which can be divided into single and multistep epitaxial growth processes.

Single step epitaxial processes. In single-step processes the full layer stack, including active and passive layers is grown in one single epitaxial step and the transparent waveguide sections are created afterwards by locally removing the active layers, as shown in figures 7(a) and (b). Figure 7(a)shows an active waveguide on top of a passive waveguide. In this approach special structures, e.g. vertical tapers, are required for coupling the light smoothly from the active to the passive waveguide and vice versa. A detailed description of a vertical integration approach is given in Menon [46] and Tolstikhin [47]. In figure 7(b) there is only one (composite) waveguide, which includes the active layer. So no vertical coupling is needed, but at the expense of a discontinuity between the active and the passive waveguide section which causes coupling loss and reflection. The discontinuity can be reduced by covering the structure with an InP cladding layer, but this requires an additional growth step.

Figure 7(c) illustrates another single-step integration method: quantum well intermixing. Here the active layer consists of a number of quantum wells. The active layer can be made passive by capping it with a material which generates vacancies in the semiconductor crystal that diffuse to the active layer when the wafer is heated. These vacancies cause the quantum well atomic species to intermix with those of the barrier layers between them which leads to an increase of the effective bandgap. Intermixing can increase the band gap wavelength of the active material by more than 100 nm, so that it becomes fully transparent. But also intermediate values are possible, e.g. for use in electro-absorption modulators. A detailed description is given by Skogen [48]. One of the disadvantages of this method is that the dopant concentrations in the active and the passive regions are the same, which causes high losses in the transparent regions. This problem can be solved by introducing an additional epitaxial step for growing an undoped cladding layer on the transparent waveguide section (blanket growth).

*Multistep epitaxial growth processes.* Single step processes are simple from an epitaxial point of view, but efficient and well controlled coupling between the active and the passive parts introduces additional complexity in the form of taper structures and/or additional growth steps. Figure 7(d) illustrates the most frequently applied approach: butt-joint integration. Here the active and passive waveguide structures are created in different growth steps, thus providing a large flexibility in the epitaxial layer structure and in the doping levels. In the past the additional growth stages could cause serious yield problems, however, with modern epitaxial technology this is no longer an issue.

In the COBRA generic process a three step epitaxial process is used to obtain the structure depicted schematically in figure 7(d), and in more detail in figure 8(a).

In a first growth step the active layer stack is grown including the lower part of the p-doped cladding. Next the active regions are masked and the exposed area is etched away. In a second selective area regrowth step the etchedaway part is replaced with a transparent waveguide stack, up to the same level as the first growth. In the transparent part the cladding layer is not doped in order to avoid absorption loss incurred by the p-dopant. In a third growth step the whole structure is covered with a p-doped cladding layer. If the regrowth process conditions are properly tuned the regrown wafer has a smooth surface and a smooth connection with low

**Figure 5.** Example of a multi-project wafer (MPW) realised in the COBRA process. The wafer contains a large number of cells with different ASPICs. The wafer has 52 cells in the usable wafer area. Each ASPIC is copied at four different locations on the wafer, so that we have room for 12 users and one test cell, which is used for wafer validation. The figure shows one cell (a test cell) and its position on the wafer. In this way, each user will receive four copies of his chip per wafer in the MPW batch. COBRA usually runs two wafers in a batch.

**Figure 6.** The dependence of chip costs on the production volume for three different manufacturing models: a vertical integrated fab model, a custom foundry model and a generic foundry model.

reflectivity between the active and the passive waveguide. Tapered and tilted interfaces are beneficial for further reduction of optical losses and reflections.

The processes at COBRA and Oclaro are very similar in outline, although different in detail. The process of Fraunhofer HHI differs more: it uses a semi-insulating (Fe-doped) substrate which leads to better rf-capabilities and enables electrical isolation of individual devices as required for example in balanced detectors. As yet it does not support the integration of optical amplifiers, but future releases of the platforms will offer a similar functionality, with differences in the technological details. In the following paragraphs we discuss a number of process enhancements that are presently being investigated.

*Reduction of waveguide loss.* In the present integration scheme, the p-doped top cladding, which is required for electrical connection to the active components, introduces an additional waveguide propagation loss of the order of 2 dB cm<sup>-1</sup> for an optimized layer stack design. In larger PICs,

which may have several centimetres of waveguide length, this introduces high losses. This loss contribution can be removed by restricting the p-doped cladding layer to the active regions, thus having no p-dopant in the transparent waveguide sections. Losses in the undoped regions are below 1 dB / cm, and the active regions are usually so short that the additional loss contribution due to the p-dopant is a few tenths of a dB at most. A locally undoped cladding layer can be realized by an additional growth step for the transparent waveguide sections or by incorporating the dopant only at the active regions by diffusion through a mask. COBRA is working on development of a low-loss generic process based on the latter approach.

Improving rf-performance. An important improvement of the performance can be obtained by fabricating the whole circuit on a semi-insulating (SI) substrate instead of an n-type substrate, as is presently already done by HHI for its highspeed receiver process. Moving from n-type to SI-substrate requires a redesign of the process, in order to replace the common n-contact at the backside of the wafer by lateral ncontacts which can be accessed from the top of the wafer. An SI-based process brings two advantages. The removal of the conductive n-type ground plane allows for higher speed operation. Both detectors and modulators on SI substrates can operate at frequencies beyond 40 GHz. Further, the n-contact layers of different components can be separated, which allows for integration of balanced photodetectors, where the p-contact from one diode is connected to the n-contact of the other. Oclaro and COBRA are both working on introduction of generic processes on SI substrates.

*Free choice of bandgap*. Another important extension of the platform capability is to allow a free choice of the bandgap of the active material. At present the same platform process can be applied to source wafers with gain sections containing different gain materials, e.g. bulk, Quantum Well or Quantum Dot layers, but only a limited number of vertical structures can be realized on the same wafer (typically 2 or 3).

**Figure 7.** Four active-passive integration schemes: (a) vertical twin-guide integration, (b) vertical single guide integration, (c) quantum well intermixing (and selective area growth), (d) butt-joint integration.

Hence, in MPW runs a choice has to be made which applies to all participants in that run, there is no flexibility within one chip or wafer.

A process offering more flexibility in bandgap properties is selective area growth (SAG). Here the growth rate in the active regions is enhanced by masking the area besides the active region. During MOVPE growth, species migrate from the masked areas to the unmasked areas where the growth rate becomes higher. If the waveguide consists of an MQW stack the wells in the active region will become thicker and this will lead to a reduction in the bandgap. The reduction can be controlled by controlling the growth enhancement via the width of the mask and the gap between the masked regions. In this way each active region can be controlled individually over a bandgap range as wide as 100 nm [49]. Because the bandgap changes are caused by a diffusion process the connection between regions with different bandgap will be smooth. In order to prevent the variations in layer thickness getting too large the SAG step is usually restricted to the active layer and the cladding layer is grown in an unmasked step. SAG thus requires multiple growth steps.

In this way a whole range of vertical structures can be designed on the same MPW which gives the designer a large degree of freedom in design of active layer properties. Firstly, the vertical structures can be optimized for multiple functionalities on the same wafer: lasers, semiconductor amplifiers, electro-absorption modulators, phase modulators, passive waveguides, etc. Secondly, the layer stacks can be optimized for each operating wavelength. For example in a WDM transmitter PIC, each laser and each electro-absorption modulator can be optimized individually for each wavelength channel. In the PARADIGM project, III-V Lab is cooperating with Fraunhofer HHI to implement this technology in a future release of their generic platform technology. In this release active MQW structures made of InGaAlAs rather than InGaAsP will be used for improved high-temperature operation.

#### 2.2. Waveguide etching

The second process module is the waveguide etching. In the COBRA process four etch steps are used for creating four different etch levels, as shown in figure 8(b). The deepest level stretches into the substrate and is used in the deep etched waveguides, in deep-etched phase modulators and detector sections (reverse biased SOA sections), and for providing

high index contrast. The deep etched waveguides are used where high contrast is essential, e.g. in small-radius bends and in compact MMI-couplers, MMI-reflectors and AWG-(de) multiplexers.

M Smit et al

The shallow etch level is used for defining shallow etched waveguides and amplifier sections, where etching through the active regions would cause increased surface recombination. Shallow waveguides show lower propagation losses due to reduced sidewall scattering; they are used for low loss interconnections.

A third etch level is applied for providing electrical isolation between different active components. The isolation is achieved by removing the highly conductive p-doped top cladding layer, down to the low-doped cladding layer just above the waveguide layer. Further, as shown in figure 3(b), this level is used in the polarization rotation sections.

The fourth and shallowest etch step is used for removing the heavily p-doped ternary (InGaAs) contact layer from the passive waveguides, where it contributes to the waveguide losses. Further, after planarization, it allows for routing electrical interconnections across the waveguides, as shown in figure 8(d). This is important because it allows routing of the electrical connections to the edge of the chip.

*DUV lithography*. The quality of the waveguides and the components based on them, such as AWGs and MMI-couplers, is strongly dependent on the quality of the lithography and the etching process. COBRA has recently installed a 193 nm DUV scanner (ASML PAS 5550/1100) with a resolution down to 90 nm. The machine has been adapted by ASML for handling 3' and 4' InP-wafers, and so far it is the only machine with this resolution worldwide that can handle InP wafers. Resolution of this machine is three times better than today's best optical lithography tools for InP-wafers (I-line steppers), which have a resolution of 250 nm.

Such an increase in resolution leads to a large increase in process performance and platform capabilities. An important advantage is that DBR and DFB gratings can be printed with fast optical lithography instead of E-beam lithography or holography. But there are more advantages. The insertion losses of AWGs will reduce from a few dB to less than 1 dB by reducing the closure of the gaps between the array waveguides. With the improved resolution the control of critical dimensions in MMI couplers and polarization converters will become much better allowing more accurate specification of device performance and leading to higher

Figure 8. Cross-section of the wafer structure after the four process modules: (a) epitaxial growth, (b) waveguide etching, (c) passivation and planarization, (d) contacting and interconnect metallization.

yield. Also, it can be expected that the waveguide propagation losses will become lower due to smoother waveguide edges.

The very thin photoresists that are used for 193 nm DUV lithography are not suited as a mask for etching thick layers and do not tolerate height steps in excess of 100 nm. As can be seen in figure 8, after the first etch step the height difference will be many times larger. Planarization steps will, therefore, be required after each etch step, similar to what is done in CMOS processing. Also the requirements on wafer flatness are tighter than those that InP substrate manufacturers can provide today. Moving from I-line to 193 nm DUV lithography requires, therefore, major adaptions of the process technology. Such process adaptions are presently being investigated by COBRA, with support of ASML.

#### 2.3. Planarization and passivation

After the etching process the sidewalls of deeply etched phase modulators and detectors have to be passivated and protected as shown in figure 8(c). In the COBRA process this is done by deposition of a polyimide layer which also reduces the height difference on the chip (planarization). The passivation layer is necessary for obtaining low dark currents in reverse biased phase modulator and detector sections. Planarization is necessary in order to facilitate subsequent lithography steps, where the large difference in height between the different mesas complicates process steps like opening of the contact regions and definition of metal contacts. The planarization layer is also used as a substrate layer for metal interconnect between electrodes and bond or probe pads. It has a welldefined height at all mesas where contacts openings have to be made and it covers the mesas where metal crossings are required for interconnect purposes.

As explained in the previous section introduction of DUV lithography imposes much more stringent requirements on the surface planarity. COBRA is working on development of chemical–mechanical polishing of a BCB planarization layer to meet those requirements.

#### 2.4. Metallization and interconnect

The last process module is for contacting and metallization as shown in figure 8(d). First the polyimide planarization layer is patterned lithographically and the remainder is etched back until the active mesas are opened. Next a thin Ti-Pt-Au contact layer is deposited with lift-off lithography for getting contacts with low series resistance. The alignment is not critical because the contacts are chosen wider than the mesa. After lift-off of the front contact the backside contact is deposited. Both contacts are annealed at the same time. For definition of bond pads and metal interconnect patterns the upper side of the wafer is covered with a thin gold seed layer, followed by a thick resist layer, which is opened where we need the metal paths. Next a thick gold pattern is electroplated through the openings in the resist mask and finally the whole gold pattern is etched back a little bit in order to remove the seed layer.

# 3. Building blocks

#### 3.1. Introduction

The basic idea behind a generic integration technology is to support the monolithic integration of a small set of accurately characterized building blocks that offer the basic functionality which is required to realize PICs for a broad range of different applications. Although the basic idea looks simple, its practical elaboration is not so straightforward, because the number of building blocks tends to become large: different types of lasers (FP, DFB, DBR, CW, pulse, tunable etc), modulators, detectors, MMI-couplers  $(1 \times 2, 2 \times 2, 1 \times 4, 2 \times 4, 4 \times 4 \text{ etc})$ and AWGs with varying numbers of channels and channel spacings, to mention just a few. To utilize the full potential of the generic integration technology these building blocks have to be accurately characterized so that users can accurately design complex circuits based on them. A user designing a circuit based on these standard components will quite rightly ask for a guarantee from the foundry that the building blocks perform according to an agreed specification. Validating the proper performance of fabricated wafers will place a huge burden on the fab if approached in the wrong way, because the whole set of building blocks should be guaranteed for each MPW. Further, with so many different building blocks it will become a complex task to optimize the integration process: which building blocks should get priority in the process development?

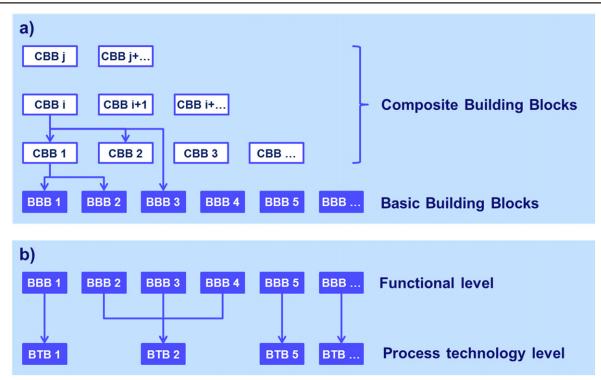

In order to make the generic process development and validation manageable we distinguish between basic building blocks (BBBs) and composite building blocks (CBBs). The idea is to identify a small number of BBBs, which can be used to construct a much larger variety of building blocks which are composed of BBBs: CBBs. In this way we create a hierarchy of building blocks in which the properties of the higher layers can be derived from the properties of the lowest layer, the BBBs. The scheme is depicted in figure 9; it will be explained in some detail in the following sections.

With this subdivision the optimization and the validation of the generic process can now be focused on a small set of building blocks: the BBBs. If their performance is optimized and validated, the performance of all PICs that are built from them according to the design rules should also meet the expectations. So instead of optimizing and validating a process for a huge number of different components, the foundry can focus all its efforts on optimizing and validating a small set of BBBs, which significantly reduces the technology development and validation burden.

# 3.2. BBBs

BBBs are the smallest (irreducible) set of functional building blocks that are required to realize the full functionality provided by the generic technology. If a building block can be decomposed in more elementary building blocks then it is not a BBB but a CBB. A laser, for example, is composed of a gain section and a resonator, so it is a CBB. The resonator itself can be formed by a ring cavity, a FP cavity (two mirrors) or a Bragg grating. For an FP-laser, for example, the BBBs are a SOA section to provide the gain, and cleaved facets to form the cavity. The SOA and the cleaved facets are BBBs since they cannot be decomposed into more elementary building blocks. A ring resonator is composed of curved and/ or straight waveguide sections, so it is a CBB. The straight and curved waveguide sections themselves are BBBs. The arrows in figure 9(a) illustrate how a CBB can be composed of a number of BBBs and/or CBBs.

Below a short description is given of the most important BBBs available in the present generic integration processes at Oclaro, Fraunhofer HHI and COBRA/SMART. Although the different processes have a lot of BBBs in common, their performance may differ, and they can also offer some building blocks that are not offered by the other platforms. Further, some building block epi-structures can be exploited to provide several different functions, a point which is expanded upon in section 3.4 below. Table 2 gives an overview of the different BBBs.

- (1) Passive waveguide section (WG). Transparent waveguide sections are the most elementary building block in any generic process. They are used for interconnects and in CBBs such as MMI-couplers and AWGs. They can be provided with different optical confinements, e.g. deep or shallow etched for strong or weak confinement. Their most important property is the propagation loss, which should be as low as possible.

- (2) SOA. An SOA is an active waveguide section which provides gain to the guided signal when an injection current is applied. Furthermore the nonlinear operation of this BBB is interesting for many applications, e.g. in alloptical switching.

- (3) Saturable absorber (SA). This is a reverse biased pindoped absorbing waveguide section, which becomes transparent if sufficient e-h pairs are generated by the absorbed light to get population inversion (bleaching). A short reverse biased SOA-section can be used as an SA.

- (4) Waveguide photo detector (PD). A waveguide PD is an absorbing waveguide section provided with electrodes to carry the photocurrent. Its structure closely resembles that of an SOA and a short reverse biased SOA section can be used as a detector.

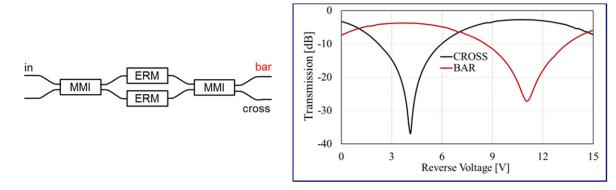

- (5) Electro-refractive modulator (ERM, ERMI). This is a pin-doped waveguide section in which a reverse (ERM) or a forward bias voltage (ERMI, current injection) induces a phase shift. The physical effects under reverse biased operation are very fast. With proper electrode design modulation as fast as  $40 \text{ Gb s}^{-1}$  is possible. With current injection the speed is restricted to a few Gb s<sup>-1</sup> by the carrier recombination time.

- (6) Electro-absorption modulator (EAM). Electro-absorption modulators are amplitude modulators. They operate at the band edge and use its bias-voltage dependence to modulate the absorption. They require a special pindoped waveguide stack with a different epitaxial structure, which is not available in the present foundry platforms. HHI has planned it for a future platform

release. Modulation speed in excess of  $40 \text{ Gb s}^{-1}$  has been reported.

- (7) Thermo-optic modulator (TOM). A thermo-optic modulator is a passive transparent waveguide section for which the phase transfer can be changed by heating it with a heater electrode on top of the waveguide. Modulation speeds are in the millisecond range.

- (8) Tunable Bragg reflector (TBR). This is a pin-doped waveguide section with a periodic corrugation for which the peak reflection wavelength can be tuned by changing the bias current. It is a key device in tunable DBR or DFB lasers.

- (9) Electrical isolation section (EI). This is a waveguide section in which the highly p-doped top cladding has been removed or made highly resistive by proton implantation. It is used, for example, for isolating a forward biased SOA section followed by a reverse biased phase modulator from each other. Without such a section electrical cross-talk will reduce circuit performance.

- (10) **Polarization rotation section** (**PR**). This is an asymmetric waveguide section (e.g. with an angled waveguide side wall) that has rotated modes and a strong birefringence. It can provide polarization rotation when properly connected to normal waveguides.

- (11) **Spot-size converter** (**SSC**). This is a BBB that adapts the size of the mode in the output waveguides of the PIC to better match the mode of a cleaved or lensed optical fibre or a dielectric interposer chip. In the current platforms these BBBs all use smoothly varying tapered waveguide cross-sections to achieve this function.

- (12) **Waveguide termination (WGT)**. This is a device which is used for coupling light out of the PIC or for providing a low or high-reflection termination. It can be a simple cleaved facet or an etched facet, straight or angled (the latter for reducing reflection), and it may contain a highreflection or anti-reflection coating.

# 3.3. CBBs

CBBs are building blocks that are composed by combining two or more BBBs and that do not require additional process steps for the combination. CBBs can be assembled by the designer using the design tools without reference to the process. For a number of them the name CBB is counterintuitive: most designers will consider a junction between two different waveguides, an MMI-coupler or a FP laser not as a CBB. As explained in the previous sections, in order to simplify the technology development and the process validation it is important to keep the number of BBBs as small as possible, and this can only be achieved if we label all components that can be formed from BBBs without further adaption of the technology as CBBs. So a laser and an MMI coupler are definitely CBBs. But also much more complex sub-circuits can serve as CBBs. Actually every sub-circuit that can be reused as a building block in other ASPICS is a CBB. To enable its re-use it is important that it is made available to other users by including it in a component library that is provided to designers in the generic process: building an extensive CBB-library is an important target for generic platform technology development.

Where the distinction between BBBs and CBBs is not relevant we will call them just building blocks. Examples of CBBs are:

- (1) Junctions between a variety of waveguides:

- Straight and curved waveguides

- Waveguides with different (or opposite) curvature as used in S-bends

- Waveguides with different widths (tapers)

- Shallow and deep waveguides

- Active and passive waveguides

- (2) MMI couplers, filters and reflectors:

- Power splitters and combiners. Special case: 3-dB couplers.

- MMI mode filters

- TE–TM splitters and combiners

- MMI-reflectors. These are MMI-couplers with a deep etched corner mirror at the end. They can be used as broadband on-chip reflectors.

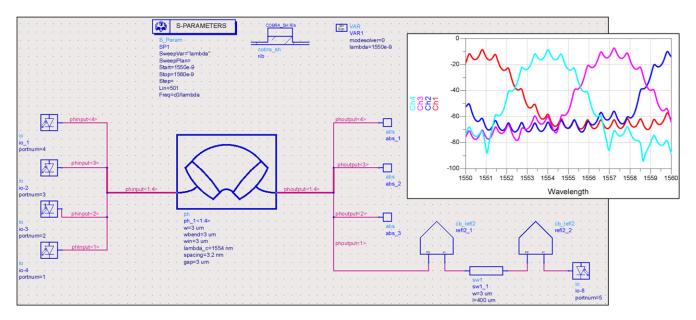

- (3) AWG (de)multiplexers. Here a large variety in device specifications is possible: multiple input and output ports, different channel spacing, free spectral range (FSR), channel passband width and shape (parabolic or flattened).

- (4) **Lasers**, such as FP lasers, tunable DFB and DBR lasers and (Mode-Locked) pulse lasers.

- (5) Mach–Zehnder or Michelson interferometer (MI) modulators and switches

- (6) Switching matrices

- (7) WDM transmitters

- (8) Advanced receiver circuits, such as DQPSK or PM-DQPSK receivers

- (9) Actually any ASPIC can be used as a CBB in a more complex ASPIC.

BBBs and CBBs are made accessible for the designers by including them in a component library. The BBB library modules are provided by the foundries. The CBB library is expected to grow continuously, with a public and a designerowned part. Designers can add their CBBs as modules to the component library and distribute them via the PDK on conditions that can be agreed between the owner of the module and the distributer of the Design Kit. In this way the library can be expanded with contributions from many designers. The potential of a generic integration technology is to a large extent dependent on the size and coverage of its CBB library.

#### 3.4. Basic technology blocks (BTBs)

BTBs are physical structures that can have different functions and that, consequently, can be used in different BBBs. An example is a SOA: a short reverse biased SOA section can also be used as a detector. In table 2, the building block structures that can serve to create a number of different functions have been labelled in **bold italics** and the BBBs that can be derived from them in *normal italics*. It is seen that by

**Figure 9.** Schematic diagram of the hierarchical structure for the different building blocks. (a) The basic building blocks offer the basic functions available on the platform. A number of BBBs can be combined in composite building blocks that perform more complex functions. They may also contain other CBBs. CBBs can have different levels of complexity, varying from a few up to a few hundred BBBs. (b) The Basic Building Blocks form the lowest functional level of the platform. At a process technology level a number of BBBs with different functions may be realized from a single structure, which we call a basic technology block.

|    |                                    |      |        | 2012   |        |        | 2015   |        |

|----|------------------------------------|------|--------|--------|--------|--------|--------|--------|

|    | Basic building blocks              | Abbr | Oclaro | HHI    | COBRA  | Oclaro | HHI    | COBRA  |

| 1  | Passive waveguide                  | WG   | •      | •      | •      | •      | •      | •      |

| 2  | Semiconductor optical amplifier    | SOA  | •      | •      | •      | •      | •      | •      |

| 3  | Photo detector                     | PD   | 10 GHz | 40 GHz | 10 GHz | 40 GHz | 40 GHz | 40 GHz |

| 4  | Saturable absorber                 | SA   | •      |        | •      | •      | •      | •      |

| 5  | Electro-refractive phase modulator | ERM  | 10 GHz |        | 10 GHz | 40 GHz |        | 40 GHz |

| 6  | Injection-type ERM                 | ERMI | 1 GHz  |        | 1 GHz  | 1 GHz  |        | 1 GHz  |

| 7  | Thermo optic phase modulator       | TOM  | •      | •      | •      | •      | •      | •      |

| 8  | Electro-absorption modulator       | EAM  |        |        |        |        | 25 GHz |        |

| 9  | Tunable Bragg reflector            | TBR  | •      |        |        | •      |        | •      |

| 10 | Electrical isolation section       | EI   | •      |        | •      | •      | •      | •      |

| 11 | Polarization Rotation section      | PR   |        |        |        |        | •      | •      |

| 12 | Spot-size converter                | SSC  | •      | •      |        | •      | •      | •      |

| 13 | Waveguide termination              | WGT  | •      | •      | •      | •      | •      | •      |

Table 2. Overview of the basic building blocks available in the three foundry platforms, at present and planned for 2015.

realizing one or more BBBs from a single BTB the number of different technology blocks that the fabs have to integrate is reduced, which also reduces the complexity of the integration technology required. However, we will need to characterize their performance individually and provide different validation criteria. We will discuss two such BTBs below.

SOAs, if operated in reverse bias, can be used as detectors. If the active layer is bulk material, the detector performance can be quite good (bandwidth >25 GHz). If the active layer is based on QW or QD-material the optical confinement

and hence the absorption is lower and the detector length needs to be longer, which reduces the bandwidth and increases the dark current. The same structure can also be used as a Saturable Absorber in a Mode-Locked Laser. By using advanced epitaxial technology that provides design freedom in the choice of the band gap of the active layer stack (SAG technology) the number of BBBs in a generic process can be even further reduced: Electro-Absorption Modulators and detectors can then also be realized in the same process as the SOAs. Electro-refractive phase modulators can be used both with reverse bias (depletion mode) and forward bias (current injection mode). Properties (electro-optic efficiency and bandwidth) will be significantly different. Further, if the electrode design is sufficiently flexible for use as a heater, they can also be used as thermo-optic modulators.

If the lithography has sufficient resolution to support first order gratings (required resolution in the order of 100 nm) the phase modulators can also be used as tunable gratings, for example in DBR lasers. Usually these gratings are realized with E-beam or holographic lithography and epitaxial overgrowth techniques. If they can be realized with side-wall gratings in the same step as the waveguides, e.g. with DUVlithography, we no longer need different technology steps for the phase modulators and the tunable gratings: they can be derived from the same modulator section used as BTB.

The BTBs lead to very useful simplification of the process technology by using a single structure for a number of different functions. Whether such combinations are possible or not depends on the specific platform technology. Because the BTBs support different functions and do not form a complete set, as illustrated in figure 9(b), the basic functionality cannot be formed by the BTBs but only at the level of the BBBs, as indicated in figure 9(b). For the designers, the functional BBB-level is the starting point for the design, and the way in which the BBBs are formed in the integration process is not relevant for them.

#### 4. BBBs

In the following paragraphs we will discuss a number of BBBs in some detail. Examples are taken from the COBRA process, because this was the first generic process that offered MPW services and most of the process and building block information is already in the public domain. They are representative of the building blocks offered by the other generic foundry processes at Oclaro and Fraunhofer HHI. Access to the COBRA process is presently offered by SMART Photonics.

Under the header Other platforms we provide for each building block some information about the most important features of the Oclaro and the Fraunhofer HHI platforms, and we also discuss ongoing work on improvements which will become available in later releases of the three platform processes.

In 2014 the JePPIX platform has launched semi-commercial access to MPW-runs on platform processes of Oclaro, the Fraunhofer HHI and SMART Photonics. Semi-commercial means that the processes are not yet fully qualified (often referred to as 'beta release' for commercial devices). Numbers and features mentioned in the present text are, therefore, a snapshot, which will be subject to change. For more actual and extensive information about the process specifications the reader is referred to the Design Manuals and the process specifications, which are available via the JePPIX platform [44] under NDA.

## 4.1. Passive waveguide sections (WG)

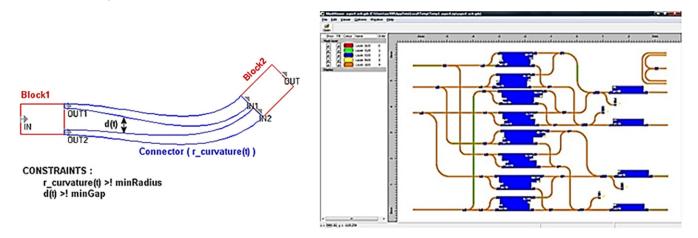

Transparent waveguide sections (WG) are the most elementary building blocks in any generic process. They are used for interconnection purposes and in CBBs like MMI-couplers and AWGs. They can be available with different optical confinements (waveguiding strengths), e.g. deep etched strongly guided (WGS) or shallow etched weakly guided (WGW). Their most important characteristic is the propagation loss, which should be as low as possible. Weakly confined waveguides usually have the lowest propagation loss and are good for interconnecting, but they do not allow for small-radius waveguide bends. Strongly confined waveguides are preferred for compact components and small bending radii, but their propagation loss is usually higher.

Figure 10 (left, middle) shows the cross-sections of a deep (strongly confined) and a shallow etched (weakly confined) waveguide in the COBRA process. The waveguide layer is a 0.5  $\mu$ m thick layer of Q1.25 bulk material. Q1.25 means lattice-matched quaternary material (InGaAsP) with a composition such that the band edge is at a wavelength of 1.25  $\mu$ m. For shallow etched waveguides the ridge is etched 100 nm into the waveguide layer. Deep etched waveguides are etched down to >150 nm below the waveguide layer. Waveguide widths can be chosen by the designer, advised standard widths are 2  $\mu$ m for shallow waveguides and 1.5  $\mu$ m for deep etched waveguides.

The propagation loss is caused by absorption losses due to free carrier absorption in the upper p-doped cladding layer and by scattering losses due to side-wall roughness of the waveguides. The cladding layers and the lower part of the waveguide layer are doped because the same waveguide structure is used in the phase modulators. The n-type dopant has no significant contribution to the losses, but the p-dopant has. The upper cladding has a stepwise graded doping profile; it is lowest close to the waveguide where it interacts most strongly with the guided mode. Its minimum level is determined by the electro-optic efficiency of the phase modulator, which requires the pn-junction to be close to the waveguide. Good e-o efficiency can be obtained with a doping level that brings a propagation loss about 2 dB cm<sup>-1</sup>. For shallow etched waveguides the scattering losses are low, total waveguide losses are about  $3 dB cm^{-1}$ . For deep etched waveguides with 1.5  $\mu$ m width the total losses are about 4 dB cm<sup>-1</sup>. Lower losses (below  $1 \text{ dB cm}^{-1}$ ) are possible with a more advanced integration process, as explained in section 2.1.

The advised minimum bend radius of the shallow etched waveguides is  $500 \,\mu$ m. Bend radii of deep etched waveguides can be as small as  $10 \,\mu$ m. Below  $50 \,\mu$ m, significant polarization conversion can occur at the junctions between straight and curved waveguide sections if the side walls are not perfectly vertical. In the COBRA process we saw no significant polarization conversion for radii down to  $20 \,\mu$ m [50].

Effective refractive indices of the shallow waveguides are in the order of 3.25 at 1550 nm wavelength. The birefringence of the shallow waveguides (effective index difference between TE-and TM-polarized modes) is in the order of  $6.10^{-3}$ , which will cause a shift in the order of 3 nm (400 GHz) in wavelength sensitive devices like AWGs and DBR gratings. For deep etched waveguides it crosses zero at a waveguide width of  $1.5 \,\mu$ m, but it is very sensitive to small width deviations. A width deviation of 50 nm already causes a (wavelength dependent) birefringence variation of a few times  $10^{-4}$ , corresponding to a TE-TM shift up to 100 GHz in an AWG.

Electrical isolation sections. The high dopant level of the upper cladding provides a resistive path between all active components connected by a waveguide, such as SOAs, detectors and modulators. If these components operate at different voltages (e.g. forward and reverse bias) large leakage currents can occur which may change the operating voltages over the components (cross-talk). To prevent such a leakage current an electrical isolation waveguide section (EI), as shown in figure 10, has to be inserted between the two components. The resistance of this section, which is strongly increased by removing the highly doped upper cladding, is in the order of  $20 \text{ k}\Omega \,\mu\text{m}^{-1}$  section length. The isolation section has slightly increased propagation loss, so it should not be made longer than necessary. The transition between a waveguide and an isolation section also introduces small additional loss. Possible reflections at this interface are reduced using an angled isolation etch.

**Other platforms.** The Oclaro platform supports only deep etched waveguides, which are identical to the Phase Modulator sections. Waveguide losses are comparable to the COBRA platform: around  $3 \text{ dB cm}^{-1}$ . The Fraunhofer HHI offers waveguides with three different etch depths (weak, medium and strong confinement). Propagation loss of the low confinement waveguides is between 0.5 and 1 dB cm<sup>-1</sup>, for the strongly confined waveguides it is in the order of 2 dB cm<sup>-1</sup>. COBRA is working on an improved platform with waveguide losses below 1 dB cm<sup>-1</sup> achieved by restricting the p-doped material to the active components (SOAs and ERMs) and avoiding it in the passive waveguides, as described in section 2.1.

# 4.2. Optical amplifiers (SOA), photo detectors (PD) and saturable absorbers (SA)

An important feature of the butt-joint epitaxial regrowth process is the modular character of the gain block: the integration process is not sensitive to the composition of the gain blocks, as long as the total thickness of the active waveguide layer is not changed. The process can be used, therefore, for bulk active layers (120 nm Q1.25 material) as well as for Quantum Well (QW) or Quantum Dot (QD) active layers with different emission wavelengths. The active layers are embedded in a Q1.25 separate confinement layer, and the total thickness of the active waveguide stack is 500 nm. All layers have their gain maximum around 1550 nm at appropriate current injection levels.

For the MPWs the COBRA process uses an MQW layer with four QWs embedded in a 500 nm Q1.25 layer. The standard SOA ridge width is  $2 \mu m$ . The SOA is shallow etched in the same etching step as the shallow waveguides. A shallow etch is applied in order to avoid the etch reaching into

the active layer, which causes increased surface recombination. Figure 11 (left) shows the cross-section. An  $800 \,\mu\text{m}$  long SOA section has a modal gain of 20 dB at an injection current of 120 mA.

For detection purposes we use a reverse biased deep etched SOA with 10  $\mu$ m width, as shown in figure 11 (middle), which allows designers to connect any shallow or deep waveguide of equal or smaller width directly to the detector. The increased width also increases the input power levels at which saturation occurs. Dark currents are lower than 1 nm nA<sup>-1</sup> detector length. With a bulk active layer a section length of 50  $\mu$ m is sufficient to absorb more than 95% of the incident light, with a QW active layer the detector becomes longer. For bulk active layers the detector capacitance and transit time are sufficiently small to allow operation speeds well beyond 10 Gb s<sup>-1</sup>, with QW active layers a special design with slightly lower responsivity is required for 10 Gb s<sup>-1</sup> operation.

The reverse biased SOA structure can also be used as a saturable absorber for use in Mode-Locked lasers.

**Other platforms.** The Oclaro platform offers excellent SOAs, which can produce up to 50 mW output power in a passive waveguide, with proper heatsinking. Modal gain at 1550 nm in a  $325 \,\mu$ m long SOA is typically  $50 \,\mathrm{cm^{-1}}$  for 15 mA injection current. The Oclaro platform offers detectors with 0.8–0.9 A W<sup>-1</sup> responsivity and 10 GHz bandwidth. The HHI platform does not support SOAs at the time of writing, an improved process with SOAs and EAMs is under development. HHI offers excellent high-speed detectors with >35 GHz bandwidth, 0.8–0.9 A W<sup>-1</sup> responsivity and dark current <5 nA (at –3 V). Because the platform uses SI substrates the detectors can be used in balanced configuration.

An important improvement of the capabilities of the platforms can obtained by introducing SAG technology which offers designers a free choice of the bandgap of active components, as described in section 2.1. HHI is working on the introduction of this technique in cooperation with III–V Lab.

# 4.3. Phase modulators (ERM, ERMI, TOM)

Figure 11 shows a schematic and an SEM photograph of the cross-section of a phase modulator. It can be realized both with a shallow or deep etched waveguide and its design is a trade-off between phase modulation efficiency in the modulator section and propagation loss in the transparent waveguide. The modulator has a pin-structure in which the phase modulation is caused by a number of effects, the most important one being carrier depletion in the waveguide layer under reverse bias. In order to optimize the phase modulation efficiency the waveguide layer is provided with a low level n-type doping  $(3.10^{-16} \text{ cm}^{-3})$ , which causes a phase modulation efficiency around  $15^{\circ} (\text{V mm})^{-1}$  in reverse bias. This requires 6-7 V for achieving  $180^{\circ}$  phase shift with a 2 mm long electrode. The modulator can operate up to  $10 \text{ Gb s}^{-1}$  with proper electrode design.

deep etched

waveguide

deep etched

waveguide

**Figure 10.** Left: cross-section of three passive basic building blocks: a shallow etched waveguide (WGW), a deep etched waveguide (PWS) and an isolation waveguide section (EI). Right: SEM photographs of a deep and a shallow etched waveguide covered with polyimide (the apparent side wall angle is due to the perspective of the SEM photograph).

The modulator section can also be used with forward bias (current injection); phase modulation efficiency is in the range of  $60^{\circ}$  mA<sup>-1</sup>, dependent on the configuration.

shallow etched

waveguide

isolation

waveguide

Thermo-optic (TO) phase modulators can be realized in the same process as the electro-optic modulators, by feeding a current through the electrodes and using their resistance to generate heat. TO modulators show a much weaker wavelength dependence than electro-refractive ones. Modulation speed is in the millisecond range. They can provide index changes of a few times  $10^{-3}$ , but they have significant power dissipation and suffer from thermal cross-talk.

In static or quasi-static applications phase modulators are often denoted as phase shifters. Technically speaking, there is no difference, except for the bandwidth, which can be low for phase shifters. In this article we will use the term modulator for both high-speed modulators and low-speed phase shifters.

**Other platforms.** The Oclaro platform offers an efficient QW phase modulator which produces  $180^{\circ}$  phase shift at 1550 nm for 3.5 V bias, in a 1 mm long modulator section. The structure supports  $10 \text{ Gb s}^{-1}$  modulation speed. In forward bias the modulator supports modulation efficiencies up to  $150^{\circ} \text{ mA}^{-1}$ . The platform also offers thermo-optic modulators, which produces  $180^{\circ}$  phase shift for 35 mW heating power in a 700  $\mu$ m long modulator section. The HHI-platform only supports TO modulators. Modulation efficiency is in the order of  $180^{\circ}$  for 25 mW in a 500  $\mu$ m long modulator section.

In the PARADIGM project Oclaro is working on an improved platform on SI-substrate offering phase modulators and detectors for 40 GBit s<sup>-1</sup>operation whilst HHI is working on the inclusion of  $25 \text{ Gb s}^{-1}$  directly modulatable (DM) lasers.

#### 4.4. TBR gratings

Tunable waveguide gratings can be used to form tunable DBR-lasers by placing them on one or both sides of a SOA gain section. They are usually formed by a periodic corrugation of the lower or upper waveguide surface, using epitaxial overgrowth after etching of the grating structure. The peak reflection wavelength can be tuned by current injection in the pin-doped waveguide. The designer can choose the peak wavelength and the reflection coefficient through the periodicity and length of the grating. In general, the coupling strength of the grating cannot be varied over the wafer, so it is fixed for a certain MPW-run, even though it could be changed between different runs.

shallow etched

waveguide

M Smit et al

The COBRA platform and the HHI-platform do not support tunable gratings at present.

**Other platforms.** The Oclaro platform supports tunable DBR sections of which the designer can choose the length and the grating pitch. Coupling strengths can be varied between 30 and  $100 \text{ cm}^{-1}$ . For the MPW-runs a value of  $50 \text{ cm}^{-1}$  is typical, but different grating strengths can be used on different wafers in the same MPW batch depending on designer requirements. The grating reflectance can be tuned by current injection over about 10 nm.

In a new release of the platform which should become available in 2015 HHI will also include SOAs and tunable gratings, for use in DBR and DFB lasers. COBRA is working on development of etched side wall gratings as shown in figure 11 (right), using its ASML DUV scanner. This innovation allows control to be released to the designer so that the grating period, length and coupling strength may be freely chosen, and the gratings are realized together with the modulators without additional process steps.

#### 4.5. Polarization rotation sections (PR)

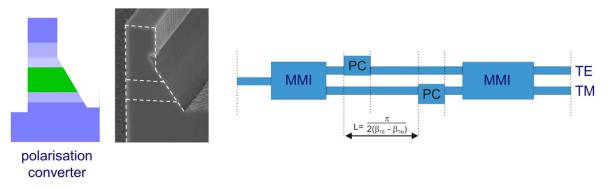

With the BBBs discussed above we can manipulate the amplitude and phase of the optical signal. A third important property of the light is its polarization. For polarization manipulation and control we need another BBB: a polarization rotation section (PR). The PR consists of a deep etched waveguide with a straight and an angled sidewall, in which the two polarization modes are rotated by 45°. When integrated between two deep etched waveguides it acts as a halfwave plate, which rotates the incoming polarization (either TE or TM) by 90°. So the combination of a polarization rotation section and two waveguide junctions acts as a polarization converter (PC). The PC is very compact: in the COBRA process a length of  $120 \,\mu m$  is sufficient to achieve the required 180° phase shift between the two orthogonally polarized modes. A polarization splitter or combiner can be realized by integrating two PCs in the arms of an MZI, as depicted in figure 12 [51]. By integrating phase shifters between a polarization splitter and a combiner we can obtain

**Figure 11.** Left: cross-section of a semiconductor optical amplifier (SOA), a waveguide photo detector (PD) and a phase modulator (ERM). Right: SEM photographs of a SOA, a phase modulator and a vertical side wall grating (the apparent side wall angle is due to the perspective of the SEM photograph).

full control over the polarization state. The PC illustrates how we can add all the functions required for on-chip polarization manipulation (polarization conversion, polarization splitting and combining, and dynamic polarization control) by adding only one BBB, a PR, to the generic integration scheme.

Polarization converters have been demonstrated at COBRA, Oclaro and HHI. At present they are not yet integrated in the generic foundry platforms because of the tight process tolerance requirements on their width.

**Other platforms.** COBRA has developed an improved PC with better process tolerance [52], which makes integration in the present technology platforms feasible. Integration of PCs is, therefore, on the roadmaps of Fraunhofer HHI and SMART Photonics. With advanced DUV lithography critical dimension (CD) control will be sufficient for supporting both the improved and the original versions of the PC.

#### 4.6. SSCs

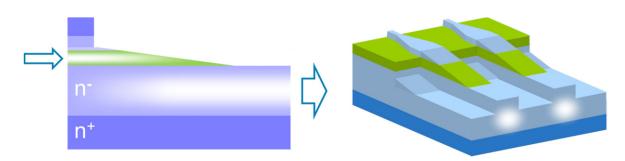

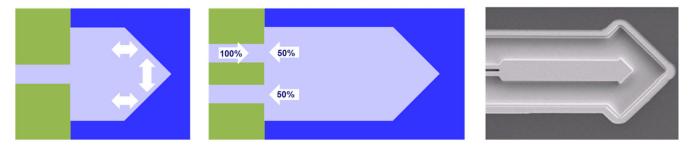

Spot size converters are crucial building blocks for efficient and tolerant coupling of light from the chip to one or more fibres. The converter acts as an optical funnel, adapting the small mode diameter of the waveguides on the chip to the mode size of a cleaved or lensed fibre. For a high coupling efficiency and good fabrication tolerance, the converter expands the horizontal and vertical diameter of the mode adiabatically.

HHI and COBRA use a similar SSC structure [53, 54]. A vertically tapered waveguide section, as depicted schematically in figure 13, forces the light from the high index passive waveguide section on top, to a low contrast fibre-matched waveguide (FMW) formed below the high index waveguide. The FMW carries a larger mode which allows for efficient and tolerant coupling to a cleaved or lensed fibre or a dielectric interposer. The FMW can be formed either by a thick  $n^-$ -doped InP layer, which has a higher refractive index then the high doped ( $n^+$ ) substrate, or as a so-called diluted waveguide by having a few (typically three) thin quaternary layers between thicker InP barrier layers.

The COBRA SSC has 0.5–1 dB coupling loss to a lensed fibre or an interposer chip with 3  $\mu$ m spot diameter and it has

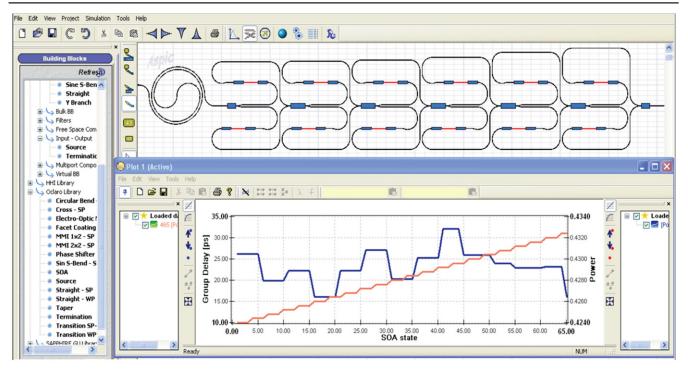

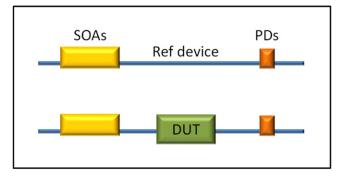

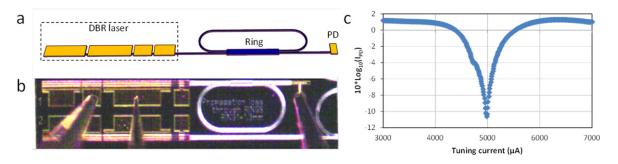

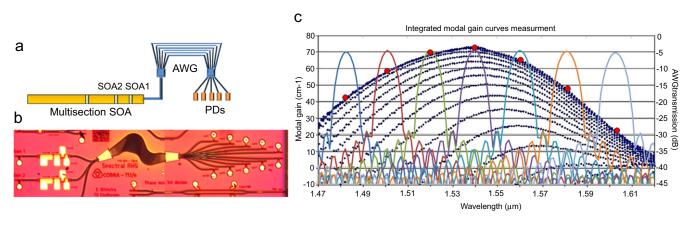

a small pitch (25  $\mu$ m), which makes it suitable for integration in dense arrays [55]. It is not yet available in MPW runs.